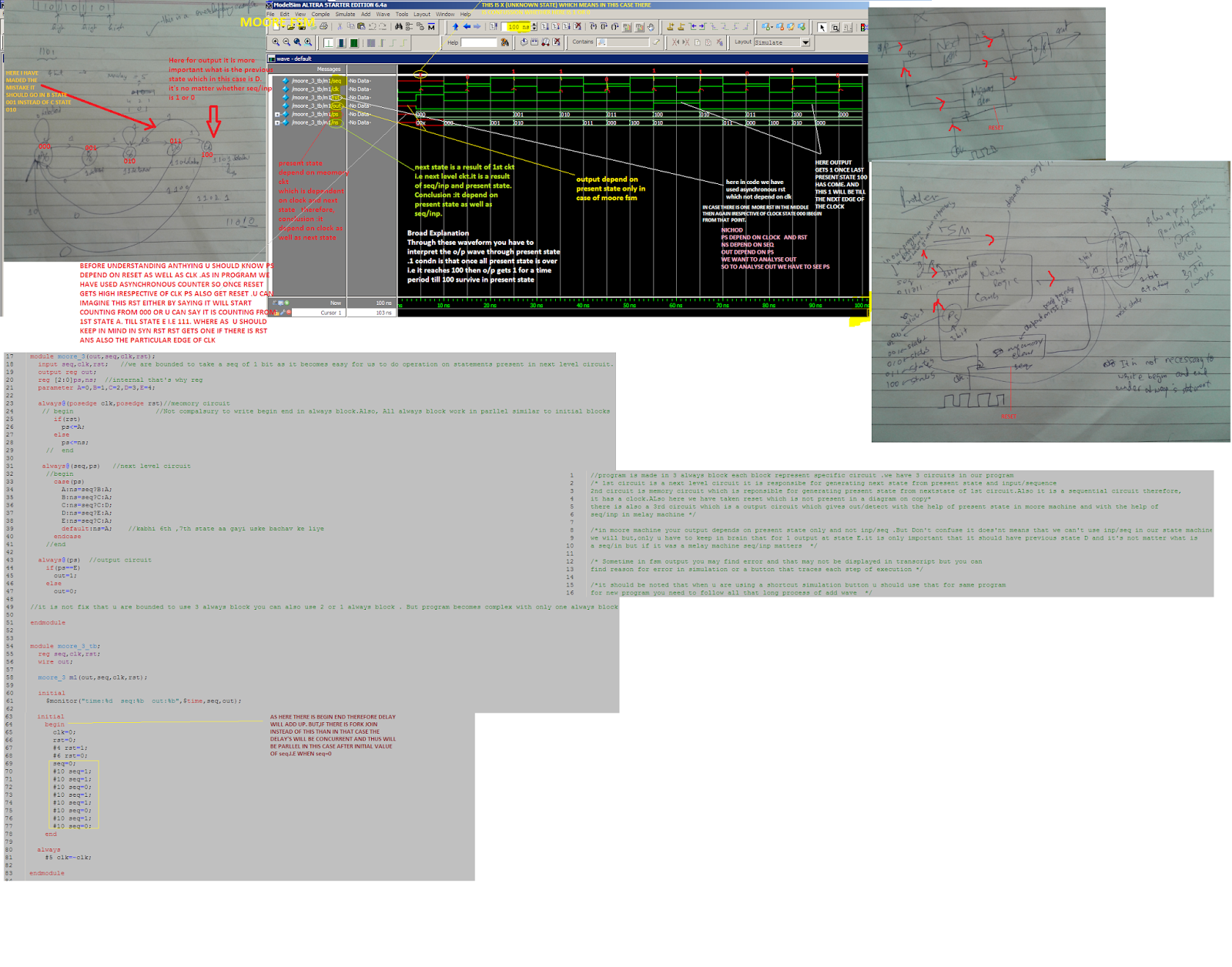

whenever you need to store value you use reg

and whenever you have to just keep value you use wire

from test bench when you provide inputs then you can say that you have provided stimulas

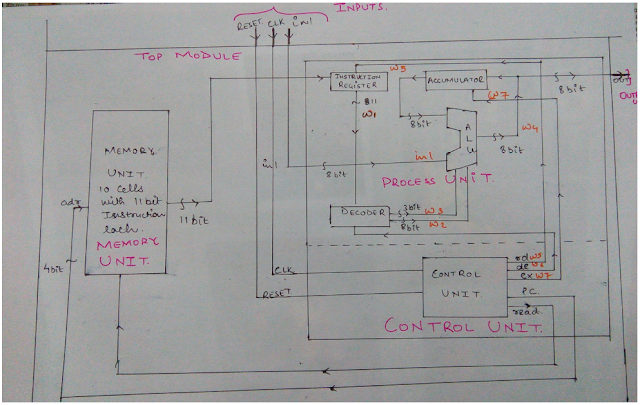

If you see the above diagram you can see that you have to provide your stored value as input in your design module so you are bouded to use reg

whereas for analyzing the output you have to use wire

You should know that tool is use tool is use to see the simulation

`include "and2.v" //we extenstion is must .v symbol

`timescale 1ns/100ps

this means it will consider #10 as 10 ns

`define clockperiodby2 10 //10ns half period is 50MHz

in above define commad you can use any name

the define command is use to assign this delay anywhere you like.For eg

clockperiodby2 clk=!clk;

when you sythesis your code in fpga you just burn design and thus there is no meaning of hash delay's .obivously as test benches are just an another way to test ur design through simulation other than FPGA. Anyway i also admity FPGA is more fun full way of testing your circuit.

It is safe to send data before posedge if you have it in your sensitiity list .Sending data after posedge makes no use

In always block you must use blocking assignment i.e <= and not "=" .However you can use any in intial block

Common Mistakes while writting test bench

Spelling of Initial

Ignoring Begin end

Anyway there are many beautiful way's of checking simulation

Using System Verilog {costilier way}--tools are crossing 1 lakh rupee

System C [Inspire from Circuit Sutra]---Basically company works on finding Verification Methodoly for Hardware design

Python scripts [Inspire from Here]