- /*module processor(a,b, );

- input [2:0]opcode;

- input a,b;

- output o;

- case(opcode)

- begin

- 000: assign o<=a+b;

- 001: assign o<a-b;

- 010: assign

- */

- module meomory(addr,,enable,out);

- input [2:0]addr; //pc

- output reg [10:0] out;

- reg [10:0]mem[7:0];

- input enable; //read

- initial

- $readmemb("input.txt",mem);

- always @(*)

- if(enable)

- out=mem[addr];

- else

- out=out;

- endmodule

- module ir(a,en,out);

- input [10:0]a;

- input en;

- output reg [10:0]out;

- always @(*)

- begin

- if(en==1)

- out=a;

- end

- endmodule

- module decoder(in,en,opcode,data);

- input [10:0]in;

- input en;

- output reg [2:0]opcode;

- output reg[7:0]data;

- always @(*)

- begin

- if(en==1)

- begin

- opcode=in[10:8];

- data=in[7:0];

- end

- /*else

- begin

- opcode=0;

- data=0;

- end*/

- end

- endmodule

- //module meomory_tb;

- // reg [3:0]addr;

- // reg enable;

- module ir_tb;

- reg [10:0]a;

- reg en;

- wire [10:0]out;

- ir v1(a,en,out);

- initial

- begin

- #1 en=1;

- #5 a=11'b10001100110;

- #10 en=0;

- #11 a=11'b01011001101;

- end

- endmodule

- module decoder_tb;

- reg [10:0]in;

- reg en;

- wire [2:0]opcode;

- wire [7:0]data;

- decoder v2(in,en,opcode,data);

- initial

- begin

- #1 en=1;

- #5 in=11'b10001100110;

- #10 en=0;

- #11 in=11'b01011001101;

- end

- endmodule

- module alu4pro(opcode,vala,valb,aluout);

- input [2:0]opcode;

- input [7:0]vala;

- input [7:0]valb;

- output reg [10:0]aluout;

- parameter add_op=3'b000,sub_op=3'b001,nand_op=3'b010,nor_op=3'b011,xor_op=3'b100,and_op=3'b101,or_op=3'b110,xnor_op=3'b111;

- always @(*)

- case(opcode)

- add_op: begin

- aluout=vala+valb;

- end

- sub_op:begin

- aluout=vala-valb;

- end

- nand_op:begin

- aluout=~(vala&valb);

- end

- nor_op:begin

- aluout=~(vala|valb);

- end

- xor_op:begin

- aluout=vala^valb;

- end

- and_op:begin

- aluout=vala&valb;

- end

- or_op:begin

- aluout=vala|valb;

- end

- xnor_op:begin

- aluout=~(vala^valb);

- end

- endcase

- endmodule

- module alu4pro_tb;

- reg [2:0]opcode;

- reg [7:0]vala;

- reg [7:0]valb;

- wire [10:0]aluout;

- alu4pro b2(opcode,vala,valb,aluout);

- initial

- begin

- opcode=3'b000;

- vala=3'b10;

- valb=3'b11;

- #20opcode=3'b110;

- vala=3'b111;

- valb=3'b101;

- end

- //$monitor("time=%d,opcode=%b,vala=%b,valb=%b,aluout=%b",$time,opcode,vala,valb,aluout);

- endmodule

- module accumulator(aluout,clk,rst,accout);

- input [7:0]aluout;

- input clk;

- input rst;

- output reg [7:0]accout;

- always@(clk)

- if(rst)

- begin

- accout=aluout;

- end

- else

- accout=0;

- endmodule

- module accumulator_tb;

- reg [7:0]aluout;

- reg clk;

- reg rst;

- wire [7:0]accout;

- accumulator b3(aluout,clk,rst,accout);

- initial

- begin

- clk=0;

- rst=1;

- aluout=6'b101011;

- #10 rst=0;

- #15 rst=1;

- end

- always #5 clk=~clk;

- endmodule

- /*module controller();

- output reg rd,rw,de,en;

- reg ps,ns;

- input clk,rst;

- always @(clk)

- */

- module controller(rst,clk,read,addr,fe,de,ex);

- input rst,clk;

- reg [2:0]ps;

- reg [2:0]ns;

- output reg read,fe,de,ex;

- parameter fetch=3'b000,decode=3'b001,execute=3'b010;

- output reg [3:0]addr=4'b0000;

- always @(posedge clk ,posedge rst)

- if (rst)

- ps<=fetch;

- else

- ps<=ns;

- always @(clk)

- case(ps)

- fetch: begin

- read=1;

- fe=0;

- de=0;

- ex=0;

- end

- decode:begin

- read=0;

- fe=0;

- de=1;

- ex=0;

- end

- execute:begin

- read=0;

- addr=addr+1;

- fe=0;

- de=0;

- ex=1;

- end

- endcase

- endmodule

- module controller_tb;

- reg rst,clk;

- //reg[2:0]ns;

- wire read;

- wire fe,de,ex;

- controller b1(rst,clk,read,fe,de,ex);

- initial

- begin

- clk=0;

- rst=0;

- #10 rst=1;

- #12 rst=0;

- // #2 ns=3'b001;

- end

- always #5 clk=~clk;

- endmodule

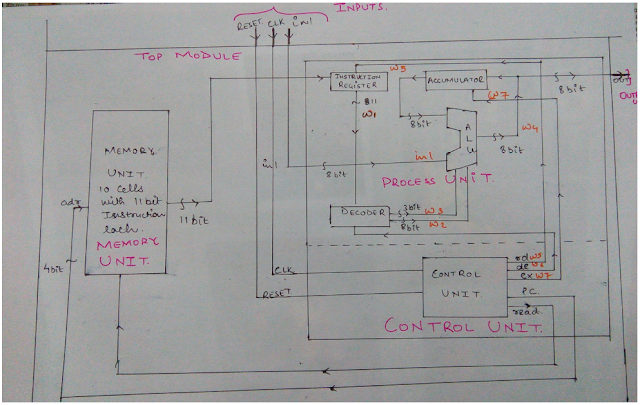

- module processor(rst,clk,inp,outp);

- input rst;

- input clk;

- input [10:0]inp;

- output [10:0]outp;

- wire accout;

- wire rd;

- wire ex;

- wire de;

- wire read;

- wire addr; //pc

- wire mout; //meomory output

- wire opcode;

- meomory hk1(addr,read,mout); //read=enable

- ir hk2(mout,rd,out); //rd-enable mout-a

- decoder hk3(out,de,opcode,data); //de-enable

- alu4pro hk4(opcode,inp,accout,aluout); //decoder ka de 8bit data kaise use karon !!!! pehle hi ek acc se i/p ek main i/p donga is module se dusra i/p decoder wale ka kya karonga ...refer to diagram

- accumulator hk5(outp,clk,ex,accout); //ex-rst

- controller hk6(rst,clk,read,addr,fe,de,ex);

- endmodule

- module processor_tb;

- reg rst,clk;

- reg[7:0]inp;

- wire [7:0]outp;

- processor hk10(rst,clk,inp,outp);

- initial

- begin

- rst=0;

- clk=0;

- #2 inp=8'b01110101;

- #5 rst=1;

- #7 rst=0;

- end

- always #10 clk=~clk;

- endmodule

simulation of proccessor_tb

Simulation of ir_tb

Simulation of decoder_tb

simulation of alu4pro_tb

simulation of controller_tb

simulation of accumulator_tb

No comments:

Post a Comment