Pages

- Blogs

- Antenna & Wave Propagation

- Electronics Devices and Circuit

- Microprocessor

- Digital Communication

- Sensors & Drivers

- Microcontroller 8051

- Telecommunication Practicals

- DICD [Practical]

- Biomedical Engineering

- EMFT

- Digital Electronics

- Project Circuits

- Robotics - Modeling and Control

- Verilog

- Embedded System Training

- UART

Sunday, 24 April 2016

Bit rate Vs Baud Rate

In digital Communication our Intention is to transfer Digital Data which is obviously seen in bit and therefore for that we use the term bit rate.

But As we can't send this digital data directly so for that we have to convert this digital data into some sought of signal and that is achieved by line coding techniques like NRZ, Manchester coding ....etc etc.

Now when we talk about speed here in sense of this signal then we talk about baud rate which is also known as pulse rate/ modulation rate/ baud rate or simply baud.

You can also make a analogy of above concept as by a example of train where each carrier of a train is the signal element (baud) and passenger sitting inside that carrier is a data element (bit).

similarly signal rate (baud rate) and data rate(bit rate)

For Higher efficieny bit rate > baud rate

and To increase this efficiency only we have many line coding techniques

Formula for Baud rate is

Baud Rate = Bit rate

------------

No. of data element carried by each signal element

There is some examples also for detail Understanding

For that [Click Here]

But As we can't send this digital data directly so for that we have to convert this digital data into some sought of signal and that is achieved by line coding techniques like NRZ, Manchester coding ....etc etc.

Now when we talk about speed here in sense of this signal then we talk about baud rate which is also known as pulse rate/ modulation rate/ baud rate or simply baud.

You can also make a analogy of above concept as by a example of train where each carrier of a train is the signal element (baud) and passenger sitting inside that carrier is a data element (bit).

similarly signal rate (baud rate) and data rate(bit rate)

For Higher efficieny bit rate > baud rate

and To increase this efficiency only we have many line coding techniques

Formula for Baud rate is

Baud Rate = Bit rate

------------

No. of data element carried by each signal element

There is some examples also for detail Understanding

For that [Click Here]

Saturday, 23 April 2016

CPU VS FPGA VS ASIC

CPU---SOFTWARE--LIST OF INSTRUCTIONS

FPGA--FIRMWARE--GATES---PROGRAMED WITH THE HELP OF VERILOG,VHDL

ASIC--IT CAN BE USED AS FPGA BUT NOT REPROGRAMMED

it means you will test your design on fpga practically verify it and then give chip manufacturing industry to manufacture a chip.

FPGA--FIRMWARE--GATES---PROGRAMED WITH THE HELP OF VERILOG,VHDL

ASIC--IT CAN BE USED AS FPGA BUT NOT REPROGRAMMED

it means you will test your design on fpga practically verify it and then give chip manufacturing industry to manufacture a chip.

Friday, 22 April 2016

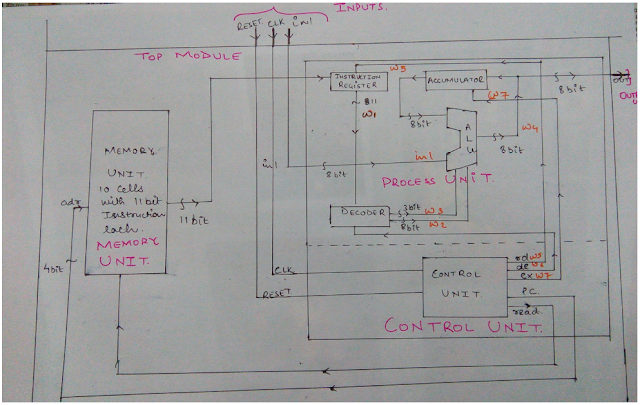

Microprocessor 8085 Verilog

- /*module processor(a,b, );

- input [2:0]opcode;

- input a,b;

- output o;

- case(opcode)

- begin

- 000: assign o<=a+b;

- 001: assign o<a-b;

- 010: assign

- */

- module meomory(addr,,enable,out);

- input [2:0]addr; //pc

- output reg [10:0] out;

- reg [10:0]mem[7:0];

- input enable; //read

- initial

- $readmemb("input.txt",mem);

- always @(*)

- if(enable)

- out=mem[addr];

- else

- out=out;

- endmodule

- module ir(a,en,out);

- input [10:0]a;

- input en;

- output reg [10:0]out;

- always @(*)

- begin

- if(en==1)

- out=a;

- end

- endmodule

- module decoder(in,en,opcode,data);

- input [10:0]in;

- input en;

- output reg [2:0]opcode;

- output reg[7:0]data;

- always @(*)

- begin

- if(en==1)

- begin

- opcode=in[10:8];

- data=in[7:0];

- end

- /*else

- begin

- opcode=0;

- data=0;

- end*/

- end

- endmodule

- //module meomory_tb;

- // reg [3:0]addr;

- // reg enable;

- module ir_tb;

- reg [10:0]a;

- reg en;

- wire [10:0]out;

- ir v1(a,en,out);

- initial

- begin

- #1 en=1;

- #5 a=11'b10001100110;

- #10 en=0;

- #11 a=11'b01011001101;

- end

- endmodule

- module decoder_tb;

- reg [10:0]in;

- reg en;

- wire [2:0]opcode;

- wire [7:0]data;

- decoder v2(in,en,opcode,data);

- initial

- begin

- #1 en=1;

- #5 in=11'b10001100110;

- #10 en=0;

- #11 in=11'b01011001101;

- end

- endmodule

- module alu4pro(opcode,vala,valb,aluout);

- input [2:0]opcode;

- input [7:0]vala;

- input [7:0]valb;

- output reg [10:0]aluout;

- parameter add_op=3'b000,sub_op=3'b001,nand_op=3'b010,nor_op=3'b011,xor_op=3'b100,and_op=3'b101,or_op=3'b110,xnor_op=3'b111;

- always @(*)

- case(opcode)

- add_op: begin

- aluout=vala+valb;

- end

- sub_op:begin

- aluout=vala-valb;

- end

- nand_op:begin

- aluout=~(vala&valb);

- end

- nor_op:begin

- aluout=~(vala|valb);

- end

- xor_op:begin

- aluout=vala^valb;

- end

- and_op:begin

- aluout=vala&valb;

- end

- or_op:begin

- aluout=vala|valb;

- end

- xnor_op:begin

- aluout=~(vala^valb);

- end

- endcase

- endmodule

- module alu4pro_tb;

- reg [2:0]opcode;

- reg [7:0]vala;

- reg [7:0]valb;

- wire [10:0]aluout;

- alu4pro b2(opcode,vala,valb,aluout);

- initial

- begin

- opcode=3'b000;

- vala=3'b10;

- valb=3'b11;

- #20opcode=3'b110;

- vala=3'b111;

- valb=3'b101;

- end

- //$monitor("time=%d,opcode=%b,vala=%b,valb=%b,aluout=%b",$time,opcode,vala,valb,aluout);

- endmodule

- module accumulator(aluout,clk,rst,accout);

- input [7:0]aluout;

- input clk;

- input rst;

- output reg [7:0]accout;

- always@(clk)

- if(rst)

- begin

- accout=aluout;

- end

- else

- accout=0;

- endmodule

- module accumulator_tb;

- reg [7:0]aluout;

- reg clk;

- reg rst;

- wire [7:0]accout;

- accumulator b3(aluout,clk,rst,accout);

- initial

- begin

- clk=0;

- rst=1;

- aluout=6'b101011;

- #10 rst=0;

- #15 rst=1;

- end

- always #5 clk=~clk;

- endmodule

- /*module controller();

- output reg rd,rw,de,en;

- reg ps,ns;

- input clk,rst;

- always @(clk)

- */

- module controller(rst,clk,read,addr,fe,de,ex);

- input rst,clk;

- reg [2:0]ps;

- reg [2:0]ns;

- output reg read,fe,de,ex;

- parameter fetch=3'b000,decode=3'b001,execute=3'b010;

- output reg [3:0]addr=4'b0000;

- always @(posedge clk ,posedge rst)

- if (rst)

- ps<=fetch;

- else

- ps<=ns;

- always @(clk)

- case(ps)

- fetch: begin

- read=1;

- fe=0;

- de=0;

- ex=0;

- end

- decode:begin

- read=0;

- fe=0;

- de=1;

- ex=0;

- end

- execute:begin

- read=0;

- addr=addr+1;

- fe=0;

- de=0;

- ex=1;

- end

- endcase

- endmodule

- module controller_tb;

- reg rst,clk;

- //reg[2:0]ns;

- wire read;

- wire fe,de,ex;

- controller b1(rst,clk,read,fe,de,ex);

- initial

- begin

- clk=0;

- rst=0;

- #10 rst=1;

- #12 rst=0;

- // #2 ns=3'b001;

- end

- always #5 clk=~clk;

- endmodule

- module processor(rst,clk,inp,outp);

- input rst;

- input clk;

- input [10:0]inp;

- output [10:0]outp;

- wire accout;

- wire rd;

- wire ex;

- wire de;

- wire read;

- wire addr; //pc

- wire mout; //meomory output

- wire opcode;

- meomory hk1(addr,read,mout); //read=enable

- ir hk2(mout,rd,out); //rd-enable mout-a

- decoder hk3(out,de,opcode,data); //de-enable

- alu4pro hk4(opcode,inp,accout,aluout); //decoder ka de 8bit data kaise use karon !!!! pehle hi ek acc se i/p ek main i/p donga is module se dusra i/p decoder wale ka kya karonga ...refer to diagram

- accumulator hk5(outp,clk,ex,accout); //ex-rst

- controller hk6(rst,clk,read,addr,fe,de,ex);

- endmodule

- module processor_tb;

- reg rst,clk;

- reg[7:0]inp;

- wire [7:0]outp;

- processor hk10(rst,clk,inp,outp);

- initial

- begin

- rst=0;

- clk=0;

- #2 inp=8'b01110101;

- #5 rst=1;

- #7 rst=0;

- end

- always #10 clk=~clk;

- endmodule

simulation of proccessor_tb

Simulation of ir_tb

Simulation of decoder_tb

simulation of alu4pro_tb

simulation of controller_tb

simulation of accumulator_tb

Scope of Chip Manufacturing

1. AI on Chip

Dhamendra Modha has written a Blog Career Opportunities in Brain-inspired Computing at IBM Research

Work Started in 2011

Dhamendra Modha has written a Blog Career Opportunities in Brain-inspired Computing at IBM Research

Top Electronics & Electrical Branch People from Whom you can Inspire .

1.Yael Maguire

2.Mayank Shrivastava

For List of Patents by him [Click Here]

As far as I make out I guess Majority of its Patent are Possible due to its Job in Infineon Technologies ic fabrication plant as experiments are difficult to do .But Anyway in today's life there are many tools like Pyxis where you do gate level modelling and test the simulations without such a plant like its Topic is

1. A DeMOS Device realized using dual STI process 8,097,930

2. A Novel Architecture for Improving Slew Rate in FinFET-based Op-Amps and OTAs 8,089,314

3. ESD Robust Drain Extended MOS Device 8,536,648

4. An IGBT device with plugged-in SCR for robust ESD protection in FinFET technology

5. "Dual Gate STI DeMOS for improved mixed signal and hot carrier behavior

6.Single Halo DeMOS for robust ESD protection in advanced high voltage CMOS

7.Nonvolatile floating gate Analog memory cell

8. High voltage semiconductor devices

9.Independently Driven Double Gate (IDDG) Nonvolatile floating gate analog memory cell

10.Novel Ways of Introducing High Voltage Handling Capabilities in FinFET Technologies 08664720

For List of Patents by him [Click Here]

As far as I make out I guess Majority of its Patent are Possible due to its Job in Infineon Technologies ic fabrication plant as experiments are difficult to do .But Anyway in today's life there are many tools like Pyxis where you do gate level modelling and test the simulations without such a plant like its Topic is

1. A DeMOS Device realized using dual STI process 8,097,930

2. A Novel Architecture for Improving Slew Rate in FinFET-based Op-Amps and OTAs 8,089,314

3. ESD Robust Drain Extended MOS Device 8,536,648

4. An IGBT device with plugged-in SCR for robust ESD protection in FinFET technology

5. "Dual Gate STI DeMOS for improved mixed signal and hot carrier behavior

6.Single Halo DeMOS for robust ESD protection in advanced high voltage CMOS

7.Nonvolatile floating gate Analog memory cell

8. High voltage semiconductor devices

9.Independently Driven Double Gate (IDDG) Nonvolatile floating gate analog memory cell

10.Novel Ways of Introducing High Voltage Handling Capabilities in FinFET Technologies 08664720

Friday, 15 April 2016

Error Checking Techniques in Data link Layer

In any communication system there is layer in the top-bottom order in one device shown below

1) Application Layer-encryption

2)Presentation Layer

3)Session Layer-check till how many pages data has sended properly

4)Transport Layer-convert big files to small messages

5)Network Layer-it adds source and destination addresses

6)Data Link Layer-it check error and also further break the messages

7)Physical Layer-Here coding techniques like NRZ-L,NRZ-M,NRZ-S,Biphase-L(Manchester coding),Biphase-M,Biphase s,Bipolar NRZ, Unipolar NRZ etc etc happen here.

at each there there is some memory containing | H | Data | T | i.e Header data tail is updated which finally have to send

Similarly other device say another mobile phone will have these layers in order

Between these devices there is a routers in which communication happen through packet switching,circuit switch,store and forward switching etc etc.

Communication Happening Between one device to another is termed as end to end communication

and Communicative Happening Between router to one particular device is Known as link to link communication.error checking,network checking happen link to link only .you thick yourself if it happens end to end how much time it have taken.Actually Every layer is linked by link to link connection i.e

Session Layer--SLP

Tansport Layer-TLP

in above short forms P stands for protocol similarly others also have some name ..search about it..

In Data Link Layer there are Many Error checking techniques

these are as follow

1)Even parity

2)Odd Parity

3)Cycle redundancy check

4)Bit Stream check-in this we divide by no. of bits and put some remainder and then store this data in tail and send.

5)check sum

and etc etc.

ODD Parity

XOR gate is a ODD parity checker as if there is a odd number of 1's then output gets 1(HIGH)

in veriog you apply XOR operation as ^(100011100)

A B OUT

0 0 0 <--Even No of 1

0 1 1 <--Odd No of 1 Output--1

1 0 1 <--Odd No of 1 Output--1

1 1 0 <--Even No of 1

Even Parity

XNOR gate is a Even parity checker as if there is a even number of 1's then output gets 1(HIGH).

in verilog you apply XNOR operation as ~^(100001111)

A B OUT

0 0 1 <--Even No of 1 Output--1

0 1 0 <--Odd No of 1

1 0 0 <--Odd No of 1

1 1 1 <--Even No of 1 Output--1

1) Application Layer-encryption

2)Presentation Layer

3)Session Layer-check till how many pages data has sended properly

4)Transport Layer-convert big files to small messages

5)Network Layer-it adds source and destination addresses

6)Data Link Layer-it check error and also further break the messages

7)Physical Layer-Here coding techniques like NRZ-L,NRZ-M,NRZ-S,Biphase-L(Manchester coding),Biphase-M,Biphase s,Bipolar NRZ, Unipolar NRZ etc etc happen here.

at each there there is some memory containing | H | Data | T | i.e Header data tail is updated which finally have to send

Similarly other device say another mobile phone will have these layers in order

Between these devices there is a routers in which communication happen through packet switching,circuit switch,store and forward switching etc etc.

Communication Happening Between one device to another is termed as end to end communication

and Communicative Happening Between router to one particular device is Known as link to link communication.error checking,network checking happen link to link only .you thick yourself if it happens end to end how much time it have taken.Actually Every layer is linked by link to link connection i.e

Session Layer--SLP

Tansport Layer-TLP

in above short forms P stands for protocol similarly others also have some name ..search about it..

In Data Link Layer there are Many Error checking techniques

these are as follow

1)Even parity

2)Odd Parity

3)Cycle redundancy check

4)Bit Stream check-in this we divide by no. of bits and put some remainder and then store this data in tail and send.

5)check sum

and etc etc.

ODD Parity

XOR gate is a ODD parity checker as if there is a odd number of 1's then output gets 1(HIGH)

in veriog you apply XOR operation as ^(100011100)

A B OUT

0 0 0 <--Even No of 1

0 1 1 <--Odd No of 1 Output--1

1 0 1 <--Odd No of 1 Output--1

1 1 0 <--Even No of 1

Even Parity

XNOR gate is a Even parity checker as if there is a even number of 1's then output gets 1(HIGH).

in verilog you apply XNOR operation as ~^(100001111)

A B OUT

0 0 1 <--Even No of 1 Output--1

0 1 0 <--Odd No of 1

1 0 0 <--Odd No of 1

1 1 1 <--Even No of 1 Output--1

Processors

DSP Processor

Keypoints that is mentioned in the video given below.But Anyway for detailed information watch just 8:26 minute video given below

Meomory -considering Ram.In Ram Meomory your size of Meomory is judged by no. of chips meomory chips present on it.

DSP processor is a chip that go into the circuit module known as PVDM's{ packet voice dsp module}.Similar to Ram Meomory no. of chips of dsp in PVDM's make me know how big is my PVDMS

DSP processor is used in your router(gateway) to convert TDM format by PSTN into IP format that is understandable by your telephone.

DSP processor also switch your organization telephone system from PSTN(G711) to WAN(G729).you can say DSP processor is used in transcode.

DSP processor is also used in conferencing between organizations seperated by WAN .both having dedicated DSP's.Moreover ,DSP also enables organization to have confrencing among there team members also via just use of router having DSP's

Keypoints that is mentioned in the video given below.But Anyway for detailed information watch just 8:26 minute video given below

Meomory -considering Ram.In Ram Meomory your size of Meomory is judged by no. of chips meomory chips present on it.

DSP processor is a chip that go into the circuit module known as PVDM's{ packet voice dsp module}.Similar to Ram Meomory no. of chips of dsp in PVDM's make me know how big is my PVDMS

DSP processor is used in your router(gateway) to convert TDM format by PSTN into IP format that is understandable by your telephone.

DSP processor also switch your organization telephone system from PSTN(G711) to WAN(G729).you can say DSP processor is used in transcode.

DSP processor is also used in conferencing between organizations seperated by WAN .both having dedicated DSP's.Moreover ,DSP also enables organization to have confrencing among there team members also via just use of router having DSP's

DSP Processor Commercial

Monday, 11 April 2016

Designing a circuits in mind.

I am visioning an Engineer who don't see the truth table of logic gates and many other devices like BJT,FET etc and test the circuit outputs directly in mind .

And Gate- Non expert person Knows that if any i/p 0 then o/p 0 but side by side to become expert you should also know if both i/p 1 o/p 1

i.e say if any i/p 0 then o/p 0

if both/all i/p 1 then o/p 1

For Nand Gate

you know it is an invert of above gate but you might don't grab below thing

i.e say if any i/p 0 then o/p 1

if both/all i/p 0 then o/p 0

Or Gate

Non expert person Knows that if any i/p 1 then o/p 1 but side by side to become expert you should also know if both i/p 0 o/p 0

i.e say if any i/p 1 then o/p 1

if both/all i/p 0 then o/p 0

similarly remember for other gates also

What More you should Know

BJT peactical working

FET practical working

Monostable

Bistable

And Gate- Non expert person Knows that if any i/p 0 then o/p 0 but side by side to become expert you should also know if both i/p 1 o/p 1

i.e say if any i/p 0 then o/p 0

if both/all i/p 1 then o/p 1

For Nand Gate

you know it is an invert of above gate but you might don't grab below thing

i.e say if any i/p 0 then o/p 1

if both/all i/p 0 then o/p 0

Or Gate

Non expert person Knows that if any i/p 1 then o/p 1 but side by side to become expert you should also know if both i/p 0 o/p 0

i.e say if any i/p 1 then o/p 1

if both/all i/p 0 then o/p 0

similarly remember for other gates also

What More you should Know

BJT peactical working

FET practical working

Monostable

Bistable

Sunday, 10 April 2016

AMBA AHB [BLOG UNDER CONSTRUCTION]

[BLOG UNDER CONSTRUCTION]

AMBA

AMBA is a bus protocol.

AMBA

AMBA is a bus protocol.

What is a protocol ?

In Practical life you can say

It is a way of communication from one entity(let mobile) to

another entity (say cloud).

Now every communication system has its specific

syntax,semantics and timing.

In Nasa Mars rover

protocol is so slow that rover data takes 1 hour to reach to the earth.

AMBA BURST

AMBA RETRY

AMBA SPLIT

Code for Master

- module ahb_master4(

- //transfer response

- input hready,

- //global signals

- input hclk,

- input hresetn, //active low

- input [1:0]hresp,

- //read data

- input [31:0]hrdata,

- input hgrant,

- //address and control

- output reg [31:0]haddr,

- output reg hwrite,

- output reg [2:0]hsize,

- output reg [2:0]hburst,

- output reg [1:0]htrans,

- output reg hreq,

- //DATA

- output reg [31:0]hwdata

- );

- reg [31:0] rhaddr;

- reg [31:0]rhrdata;

- reg [31:0] mem[8:0]; //it means it has nine meom loc under which there is further 32 locations

- reg [2:0] ps,ns;

- integer count;

- parameter idle=3'b000,trans=3'b001,check=3'b010,Nonseq=3'b011,Seq=3'b100,Write=3'b101,Read=3'b110;

- always @(posedge hclk)

- begin

- $readmemb("memory.txt",mem);

- case(ps)

- idle : begin

- if(!hresetn)

- begin

- haddr=0;

- hsize=0;

- hburst=0;

- htrans=0;

- hwdata=0;

- hwrite=1;

- ns=idle;

- end

- else if(hready & !hresp)

- begin

- hreq=1'b1;

- ns=trans;

- end

- end

- trans : begin

- if(hready & hgrant & !hresp)

- begin

- htrans<=2'b10;

- haddr<=32'd00;

- rhaddr<=haddr;

- hburst<=3'b010;

- hwrite<=1;

- hsize<=3'b010;

- ns=check;

- end

- else

- ns=idle;

- end

- check : begin

- if(hready & !hresp) begin

- if(htrans==2'b10)

- begin

- ns=Nonseq;

- count=0;

- end

- else if(htrans==2'b11)

- begin

- ns=Seq;

- count=0;

- end

- else if(htrans==2'b00)

- ns=idle;

- end

- end

- Nonseq : begin

- if((hgrant==1'b1) & hready & !hresp)

- begin

- /*haddr<=haddr;

- hburst<=3'b000;

- hsize<=3'b010;

- hwrite<=0;

- end*/

- if(hwrite)

- ns=Write;

- else

- ns=Read;

- end

- end

- Seq : begin

- if((hgrant==1'b1) && hready && !hresp && htrans!=2'b01) //Busy transfer htrans=2'b01

- begin

- htrans=2'b11;

- case(hburst)

- 3'b000 : haddr=haddr; //Single Burst

- 3'b001 : begin //Incrementing Burst with undefined length

- count=count+1;

- if(hsize==3'b000)

- haddr=haddr+1;

- else if(hsize==3'b001)

- haddr=haddr+2;

- else if(hsize==3'b010)

- haddr=haddr+4;

- end

- 3'b010 : begin

- count=count+1; //Wrapping Burst with 4 beats

- if(hsize==3'b000)

- begin

- haddr=haddr+1;

- if(haddr==rhaddr+16)

- haddr=rhaddr;

- end

- else if(hsize==3'b001)

- begin

- haddr=haddr+2;

- if(haddr==rhaddr+16)

- haddr=rhaddr;

- end

- else if(hsize==3'b010)

- begin

- haddr=haddr+4;

- if(haddr==rhaddr+16)

- haddr=rhaddr;

- end

- end

- 3'b011 : begin

- count=count+1; // Incrementing Burst with 4 beats

- if(hsize==3'b000)

- haddr=haddr+1;

- else if(hsize==3'b001)

- haddr=haddr+2;

- else if(hsize==3'b010)

- haddr=haddr+4;

- end

- 3'b100 : begin

- count=count+1;

- if(hsize==3'b000) //8 Beat wrapping burst

- begin

- haddr=haddr+1;

- if(haddr!=rhaddr+32)

- haddr=rhaddr;

- end

- else if(hsize==3'b001)

- begin

- haddr=haddr+2;

- if(haddr!=rhaddr+32)

- haddr=rhaddr;

- end

- else if(hsize==3'b010)

- begin

- haddr=haddr+4;

- if(haddr!=rhaddr+32)

- haddr=rhaddr;

- end

- end

- 3'b101 : begin

- count=count+1; // Incrementing Burst with 8 beats

- if(hsize==3'b000)

- haddr=haddr+1;

- else if(hsize==3'b001)

- haddr=haddr+2;

- else if(hsize==3'b010)

- haddr=haddr+4;

- end

- 3'b110 : begin

- count=count+1;

- if(hsize==3'b000) //16 Beat wrapping burst

- begin

- haddr=haddr+1;

- if(haddr!=rhaddr+64)

- haddr=rhaddr;

- end

- else if(hsize==3'b001)

- begin

- haddr=haddr+2;

- if(haddr!=rhaddr+64)

- haddr=rhaddr;

- end

- else if(hsize==3'b010)

- begin

- haddr=haddr+4;

- if(haddr!=rhaddr+64)

- haddr=rhaddr;

- end

- end

- 3'b111 : begin

- count=count+1; // Incrementing Burst with 16 beats

- if(hsize==3'b000)

- haddr=haddr+1;

- else if(hsize==3'b001)

- haddr=haddr+2;

- else if(hsize==3'b010)

- haddr=haddr+4;

- end

- endcase

- if(hwrite)

- ns=Write;

- else

- ns=Read;

- end

- else if(hresp==2'b10)

- begin

- htrans=0;

- ns=idle; end

- else if(hresp==2'b11)

- begin ns<=ps; htrans<=0; end

- end

- Write : begin

- if(hready & !hresp) begin

- if(hsize==3'b000)

- begin

- hwdata[7:0]=mem[7];

- end

- else if(hsize==3'b001)

- begin

- hwdata[15:0]=mem[5];

- end

- else if(hsize==3'b010)

- begin

- hwdata=mem[2];

- end

- if(hburst!=0)

- begin

- if(hburst==3'b001)

- ns=Seq;

- else if((hburst==3'b010 | hburst==3'b011) & count<3)

- ns=Seq;

- else if((hburst==3'b100 | hburst==3'b101) & count<7)

- ns=Seq;

- else if((hburst==3'b110 | hburst==3'b111) & count<15)

- ns=Seq;

- else

- ns=idle;

- end

- else

- ns=idle;

- end

- end

- Read :begin if(hready & !hresp)

- begin

- if(hsize==3'b000)

- begin

- rhrdata=hrdata[7:0];

- end

- else if(hsize==3'b001)

- begin

- rhrdata=hrdata[15:0];

- end

- else if(hsize==3'b010)

- begin

- rhrdata=hrdata;

- end

- if(hburst!=0)

- begin

- if(hburst==3'b001)

- ns=Seq;

- else if((hburst==3'b010 | hburst==3'b011) & count<3)

- ns=Seq;

- else if((hburst==3'b100 | hburst==3'b101) & count<7)

- ns=Seq;

- else if((hburst==3'b110 | hburst==3'b111) & count<15)

- ns=Seq;

- else

- ns=idle;

- end

- else

- ns=idle;

- end

- end

- endcase

- end

- always@(posedge hclk)

- begin

- if(!hresetn)

- ps<=idle;

- else

- ps<=ns;

- end

- endmodule

Testbench for Master

- module ahb_master4_tb;

- // Inputs

- reg hready;

- reg hclk;

- reg hresetn;

- reg [1:0]hresp;

- reg [31:0] hrdata;

- reg hgrant;

- // Outputs

- wire [31:0] haddr;

- wire hwrite;

- wire [2:0] hsize;

- wire [2:0] hburst;

- wire [1:0] htrans;

- wire hreq;

- wire [31:0] hwdata;

- // Instantiate the Unit Under Test (UUT)

- ahb_master4 uut (

- .hready(hready),

- .hclk(hclk),

- .hresetn(hresetn),

- .hresp(hresp),

- .hrdata(hrdata),

- .hgrant(hgrant),

- .haddr(haddr),

- .hwrite(hwrite),

- .hsize(hsize),

- .hburst(hburst),

- .htrans(htrans),

- .hreq(hreq),

- .hwdata(hwdata)

- );

- initial begin

- // Initialize Inputs

- hready = 0;

- hclk = 0;

- hresetn = 0;

- hresp = 0;

- hrdata = 0;

- hgrant = 0;

- // Wait 100 ns for global reset to finish

- #100;

- hready <= 1;

- hresetn <= 1;

- hresp <= 0;

- hrdata <= 32'd4100450780;

- hgrant <= 1;

- // Wait 100 ns for global reset to finish

- #200;

- hready <= 1;

- hresetn <= 1;

- hresp <= 0;

- hrdata <= 32'd4123450460;

- hgrant <= 1;

- #200;

- hready <= 0;

- hresetn <= 1;

- hresp <= 0;

- hrdata <= 32'd4123450461;

- hgrant <= 1;

- // Wait 100 ns for global reset to finish

- #200;

- hready <= 1;

- hresetn <= 1;

- hresp <= 2'b11;

- hrdata <= 32'd4123450461;

- hgrant <= 1;

- // Wait 100 ns for global reset to finish

- #200;

- hready <= 1;

- hresetn <= 1;

- hresp <= 0;

- hrdata <= 32'd4123450461;

- hgrant <= 1;

- end

- always #20 hclk=~hclk;

- initial

- $monitor("time=%d,hready=%b,read_data=%d,address=%d",$time,hready,uut.rhrdata,haddr);

- // Add stimulus here

- endmodule

Code for slave

- module ahb_slave2(

- input hsel,

- //Address and control

- input [31:0]haddr,

- input hwrite,

- input [1:0]htrans,

- input [2:0]hsize,

- input [2:0]hburst,

- //Data

- input [31:0]hwdata,

- //Global Signal

- input hclk,

- input hresetn,

- //Output signals

- output reg hready,

- output reg [1:0]hresp,

- output reg [31:0]hrdata

- );

- reg rhsel;

- reg [31:0]rhaddr;

- reg rhwrite;

- reg [1:0]rhtrans;

- reg [2:0]rhsize;

- reg [2:0]rhburst;

- reg [31:0]mem[12:0];

- always @(posedge hclk,negedge hresetn)

- begin

- if(!hresetn)

- begin

- rhsel<=hsel;

- rhaddr<=0;

- rhwrite<=0;

- rhtrans<=0;

- rhsize<=0;

- rhburst<=0;

- hready<=1;

- hresp<=0;

- end

- else if(rhsel)

- begin

- rhaddr<=haddr;

- rhwrite<=hwrite;

- rhtrans<=htrans;

- rhsize<=hsize;

- rhburst<=hburst;

- hready=1;

- end

- end

- always @(posedge hclk,rhaddr)

- begin

- if(rhsel && rhwrite)

- begin

- if(rhsize==3'b000)

- mem[rhaddr[29:0]]=hwdata[7:0];

- else if(rhsize==3'b001)

- mem[rhaddr[29:0]]=hwdata[15:0];

- else if(rhsize==3'b010)

- mem[rhaddr[29:0]]=hwdata;

- if(rhaddr<=12) begin

- hready=1;

- hresp=0;

- end

- else begin

- hready=0;

- hresp=2'b01;

- end

- end

- else if(rhsel && !rhwrite)

- begin

- if(rhsize==3'b000) begin

- hrdata[7:0]=8'd13;

- hrdata[31:8]=24'bx; end

- else if(rhsize==3'b001) begin

- hrdata[15:0]=16'd34;

- hrdata[31:16]=16'bx; end

- else if(rhsize==3'b010)

- hrdata=32'd134;

- if(rhaddr<=12) begin

- hready=1;

- hresp=0;

- end

- else begin

- hready=0;

- hresp=2'b01;

- end

- end

- end

- endmodule

Test Bench for Slave

- module ahb_slave2_tb;

- // Inputs

- reg hsel;

- reg [31:0] haddr;

- reg hwrite;

- reg [1:0] htrans;

- reg [2:0] hsize;

- reg [2:0] hburst;

- reg [31:0] hwdata;

- reg hclk;

- reg hresetn;

- // Outputs

- wire hready;

- wire [1:0] hresp;

- wire [31:0] hrdata;

- // Instantiate the Unit Under Test (UUT)

- ahb_slave2 uut (

- .hsel(hsel),

- .haddr(haddr),

- .hwrite(hwrite),

- .htrans(htrans),

- .hsize(hsize),

- .hburst(hburst),

- .hwdata(hwdata),

- .hclk(hclk),

- .hresetn(hresetn),

- .hready(hready),

- .hresp(hresp),

- .hrdata(hrdata)

- );

- initial begin

- // Initialize Inputs

- hsel = 1;

- haddr = 0;

- hwrite = 0;

- htrans = 0;

- hsize = 0;

- hburst = 0;

- hwdata = 0;

- hclk = 0;

- hresetn = 0;

- // Wait 100 ns for global reset to finish

- #100;

- hsel = 1;

- haddr = 32'd00;

- hwrite = 1;

- htrans = 2'b10;

- hsize = 3'b010;

- hburst = 3'b010;

- hwdata = 32'd49;

- hresetn = 1;

- // Wait 100 ns for global reset to finish

- #100;

- hsel = 1;

- haddr = 32'd04;

- hwrite = 1;

- htrans = 2'b11;

- hsize = 3'b010;

- hburst = 3'b010;

- hwdata = 32'd45;

- hresetn = 1;

- // Wait 100 ns for global reset to finish

- #100;

- hsel = 1;

- haddr = 32'd08;

- hwrite = 1;

- htrans = 2'b11;

- hsize = 3'b010;

- hburst = 3'b010;

- hwdata = 32'd47;

- hresetn = 1;

- // Wait 100 ns for global reset to finish

- #100;

- hsel = 1;

- haddr = 32'd12;

- hwrite = 1;

- htrans = 2'b11;

- hsize = 3'b010;

- hburst = 3'b010;

- hwdata = 32'd43;

- hresetn = 1;

- // Add stimulus here

- end

- always #50 hclk=~hclk;

- endmodule

Code for AHB

- module ahb(

- input hclk,

- input hresetn,

- input hgrant,

- output reg hreq,

- input hsel

- );

- wire hready;

- wire [1:0]hresp;

- wire hwrite;

- wire [31:0]haddr;

- wire [31:0]hwdata;

- wire [31:0]hrdata;

- wire [2:0]hsize;

- wire [2:0]hburst;

- wire [1:0]htrans;

- ahb_master4 m1(hready,hclk,hresetn,hresp,hrdata,hgrant,haddr,hwrite,hsize,hburst,htrans,hreq,hwdata);

- ahb_slave s1(hsel,haddr,hwrite,htrans,hsize,hburst,hwdata,hclk,hresetn,hready,hresp,hrdata);

- endmodule

Code for AHB test bench

module ahb_tb;

- // Inputs

- reg hclk;

- reg hresetn;

- reg hgrant;

- reg hsel;

- // Outputs

- wire hreq;

- // Instantiate the Unit Under Test (UUT)

- ahb uut (

- .hclk(hclk),

- .hresetn(hresetn),

- .hgrant(hgrant),

- .hreq(hreq),

- .hsel(hsel)

- );

- initial begin

- // Initialize Inputs

- hclk = 0;

- hresetn = 0;

- hgrant = 0;

- hsel = 0;

- // Wait 100 ns for global reset to finish

- #200;

- hresetn =0;

- hgrant = 1;

- hsel = 1;

- // Wait 100 ns for global reset to finish

- #100;

- // Add stimulus here

- hresetn = 1;

- hgrant = 1;

- hsel = 1;

- // Wait 100 ns for global reset to finish

- end

- always #50 hclk=~hclk;

- endmodule

Battery Charging Circuits

In your Home Socket there comes an AC that you convert into DC using your adapter [AC-->Transformer[Coils Mutual Induction] {for step down} + Rectifier [wave shaping circuits] + Capacitor-->DC]

once DC come out of Adapter Via USB you charge your battery

Between USB port and battery there is some circuit that charges the Battery which is embedded with many features.

Q What are these Circuits Responsible for ?

Ans . Many things like

1) Battery protection circuit-Sometime Battery itself featured by this function.Sometime we have to provide this function using some special circuitry like using IC-DW01A

beside this function there is many more fuction .To Know about it Watch the Video that is provided in the end.

For Detailed In-depth Understanding about TP4056 Watch the Video Shown below

once DC come out of Adapter Via USB you charge your battery

Between USB port and battery there is some circuit that charges the Battery which is embedded with many features.

Q What are these Circuits Responsible for ?

Ans . Many things like

1) Battery protection circuit-Sometime Battery itself featured by this function.Sometime we have to provide this function using some special circuitry like using IC-DW01A

beside this function there is many more fuction .To Know about it Watch the Video that is provided in the end.

Q What Kind of Circuits/IC's that are currently available in the Market to charge battery via USB ?

Ans

- MCP73831-charge 0.5 A

- TP4056 -charge 1 A [Recoccmended for LiPos Battery] {LiPos are rectangular shaped batteries where as Lions are cylinderical shaped Batteries }

Buy TP4056 at Rs 119/- from Ebay [Click Here] to Buy One

For Detailed In-depth Understanding about TP4056 Watch the Video Shown below

Subscribe to:

Comments (Atom)